一. 封测定义

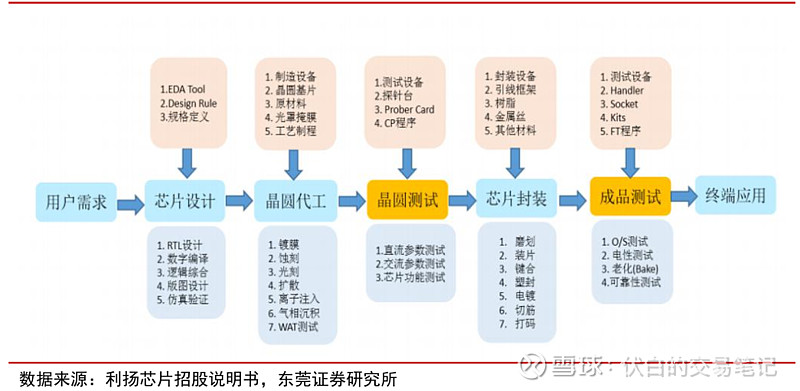

集成电路产业链可分为芯片设计、晶圆制造、封装测试三大环节。封测包括封装和测试两个环节。

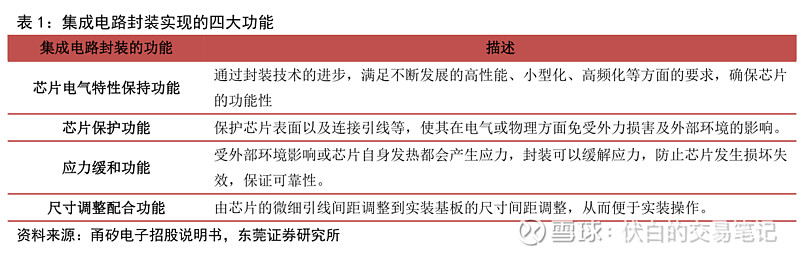

集成电路封装 :将晶圆片进行切割、焊线,使芯片电路与外部器件实现电气连接。主要有电气特性保持、芯片保护、应力缓和、尺寸调整配合四大功能。

集成电路测试 :对芯片产品的性能和功能进行测试,测试合格后,芯片成品即可使用。

测试环节可以确保芯片良率、减少封装成本;测试数据可以用于指导芯片设计和封装环节的工艺改进。

按测试内容分类,集成电路测试可分为参数测试和功能测试。

芯片产业链相关阅读:《芯片(集成电路)产业链框架及个股梳理》

二. 行业竞争格局

封测作为半导体下游环节,受半导体市场及终端消费市场需求波动影响,存在较为明显的周期特性。

封测的附加价值相对低,劳动密集度高,是国产化最高的环节。全球前十国内占据三席:长电科技(第三)、通富微电(第五)、华天科技(第六)。

全球营收前十大封测厂商排名:日月光(台)、安靠(美)、长电科技、力成(台)、通富微电、华天科技、智路封测(新加坡)、京元电子(台)、南茂(台)、顾邦(台)。

三. 发展趋势:先进封装

随着台积电宣布2nm制程工艺实现突破,集成电路制程工艺已接近物理尺寸极限,行业进入后摩尔时代。

由于集成电路制程工艺短期内难以突破,通过先进封装技术提升芯片整体性能成为了集成电路行业技术发展趋势。

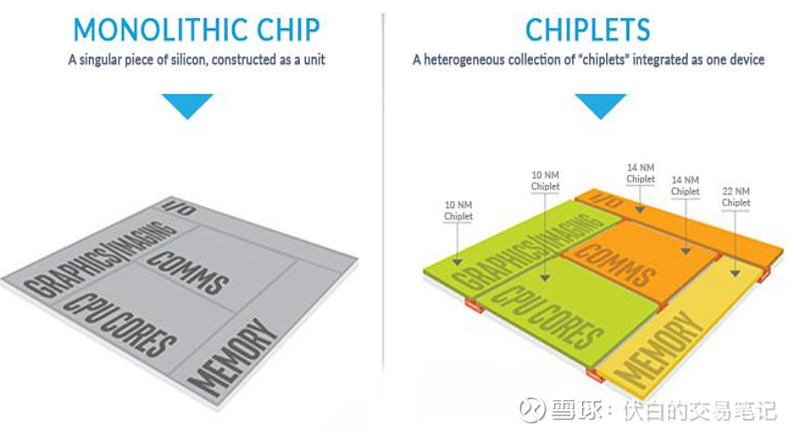

Chiplet 是依托高级封装技术实现芯片性能提升、成本可控的高效架构设计模式 。

Chiplet方案将IP核切分为可模块化组装的小裸片(die),分别进行独立制造,再通过先进封装技术实现系统级封装:

3.1 Chiplet可大幅提高芯片良率

更高算力需求和更大存储使得芯片面积急剧增大。芯片良率随着芯片面积增大而下降。

3.2 Chiplet有利于降低设计的复杂度和设计成本

Chiplet将小芯片组合封装形成一个大的单片芯片。利用小芯片的低工艺和高良率可以有效降低成本开销。

3.3 Chiplet可降低芯片制造成本

不同的芯粒可以选择合适的工艺制程分开制造,不需要全部都采用先进制程在一块晶圆上制造,大幅降低芯片的制造成本。

相关阅读:《Chiplet(芯粒)技术前瞻解析》

四. 国内标的

长电科技:国内第一、全球第三的半导体封测企业,重点发展系统级(SiP)、晶圆级和2.5D/3D等先进封装技术。

通富微电:国内第二、全球第五的半导体封测企业,已大规模生产Chiplet产品,7nm产品已量产,5nm产品已完成研发。

华天科技:国内第三、全球第六的半导体封测企业,AMD 最大的封装测试供应商。具备chiplet技术平台,Chiplet系列已实现量产。

晶方科技:主营传感器领域的封测服务,全球第二大提供WLCSP量产服务的封测服务商。产品主要有影像传感芯片、光感应芯片、医疗电子器件、MEMS、生物身份识别芯片等