今年的OFC大会上,来自Meta的Matthew Traverso做了题为"Advancement in CPO and Ecosystem"的邀请报告,系统地梳理了芯片大厂在CPO领域的进展。小豆芽这里整理下相关信息,供大家参考。

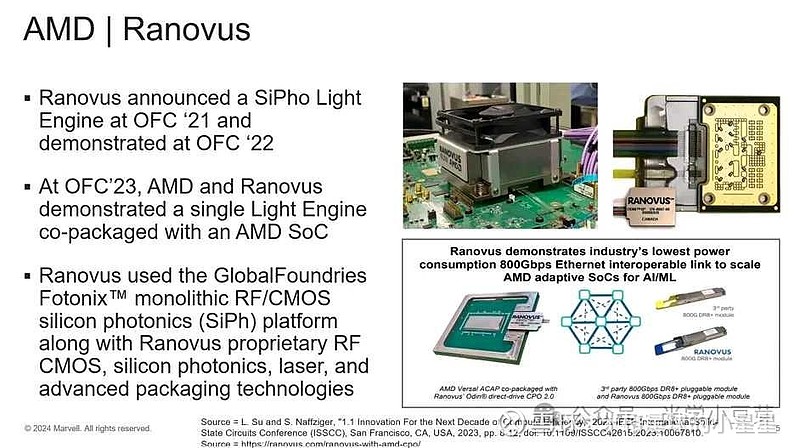

1. AMD与Ranovus

Xilinx与Ranovus合作多年,并在OFC2023上展示了Ranovus的800G直驱硅光引擎与AMD的FPGA芯片(Xilinx Versal ACAP)封装在一起的系统。Ranovus在CPO领域经营多年,主要的技术亮点在采用量子点激光器、微环调制器等。Ranovus最近也与联发科展开CPO相关的合作, 发布了其最新一代的6.4Tbps光引擎。关于Ranovus CPO的技术细节,小豆芽后续单独介绍。

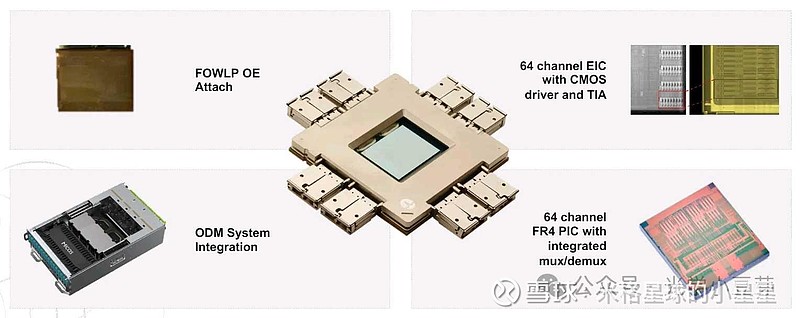

2. Broadcom

Broadcom在今年OFC上展示了带有CPO的51.2T交换机系统,系统中含有8个6.4T的FR4光引擎。单个光引擎中包含64通道的PIC与EIC芯片,driver/TIA采用CMOS工艺,单通道信号速率为100Gbps。PIC上片上集成了Mux/DeMux,工作波长为CWDM4。光引擎采用的是FOWLP封装方案,先前采用的是TSV方案,这可能主要是成本与良率的考量。关于Broadcom CPO的具体细节,可以参看小豆芽先前的笔记,这里不再赘述(Broadcom的CPO进展, Broadcom的CPO进展(续))。Broadcom与腾讯展开合作,在其数据中心中部署带有CPO的网络交换机。

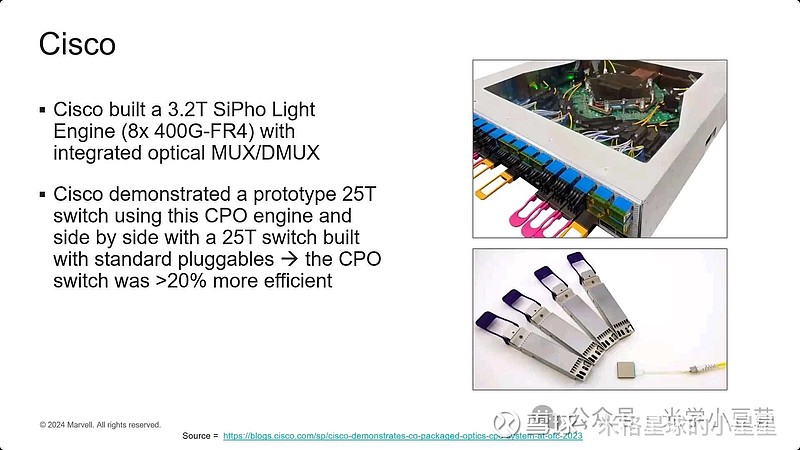

3. Cisco

Cisco在OFC2023展示过其基于CPO的25.6T交换机原型机。系统中包含8个3.2T硅光光引擎,单个光引擎中采用8个400G-FR4硅光芯片,单通道速率为100Gbps, 采用的是SISCAP型调制器,片内集成了Mux/DeMux。

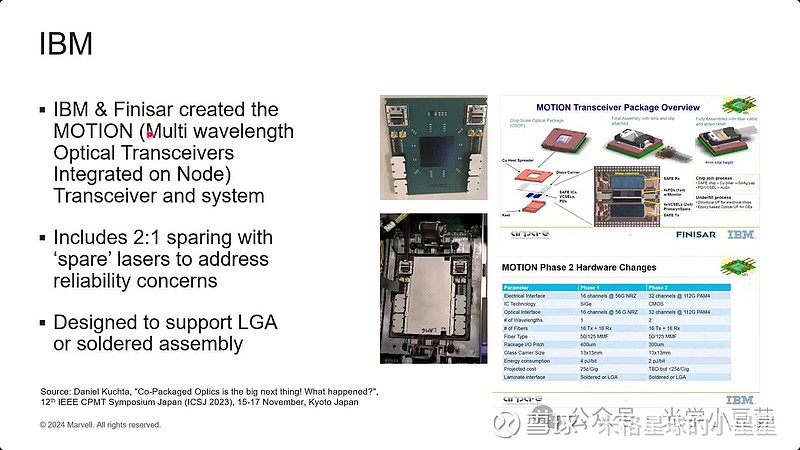

4. IBM

IBM独树一帜,没有采用硅光方案,而是与Finisar合作,开发了基于VCSEL的CPO系统(OFC 2023: 基于VCSEL的CPO进展)。系统中包含4颗PD芯片,4颗VCSEL芯片。为了系统可靠性的考量,每个VCSEL配置了一个冗余的VCSEL。单通道信号速率为56G NRZ, 共16通道,总带宽为896Gbps。光引擎可以与基板采用LGA或者焊接的方式进行连接。

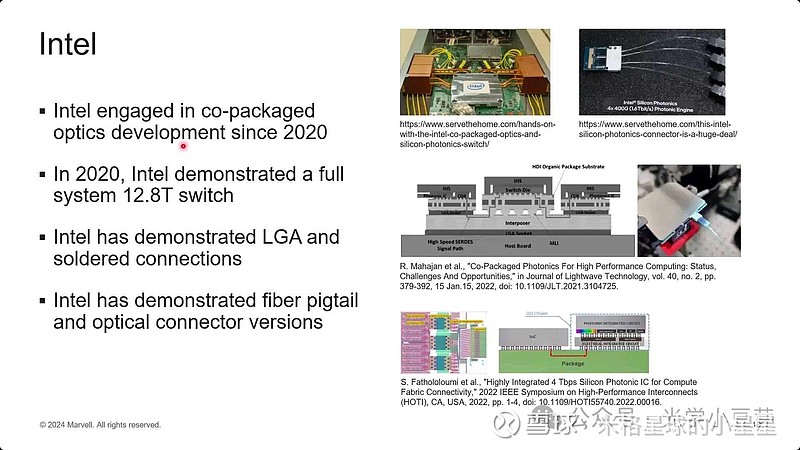

5. Intel

Intel在硅光领域深耕多年,此前主要侧重硅光的可插拔光模块以及微环调制器技术的研发。从2020年开始在CPO领域布局,瞄准Optical Compute Inteconnect(OCI),利用其特有的硅光工艺平台,开发了基于微环调制器的CPO系统。在今年OFC上,更是展示了其最新的OCI进展,单颗PIC上有64条光学通道,单链路的信号速率为32Gbps,整体的信号带宽为2Tbps(双向带宽为4Tbps),链路误码率小于1e-12。此外Intel开发了特有的可插拔光连接器,可以在封装前对PIC芯片进行筛选,进而提高良率,为CPO的大规模量产奠定了基础。关于Intel CPO的技术细节,可以参看小豆芽先前的多篇笔记: OFC2024: Intel发布最新optical IO进展, Intel的可插拔光连接器揭秘。

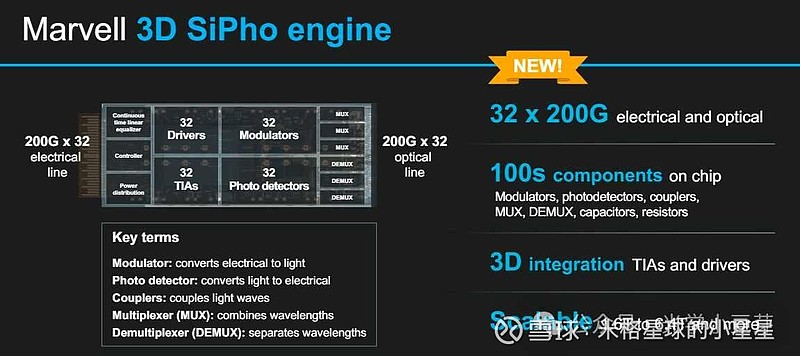

6. Marvell

Marvell在收购Inphi之后,大大增强了其在光通信和数据中心领域的研发实力。Marvell在今年OFC上推出了最新的6.4T 3D封装硅光引擎,包含32个通道,单通道信号速率为200Gbps。关于Marvell硅光光引擎的技术细节,可以参看 Marvell的异质集成2.5D硅光光引擎。

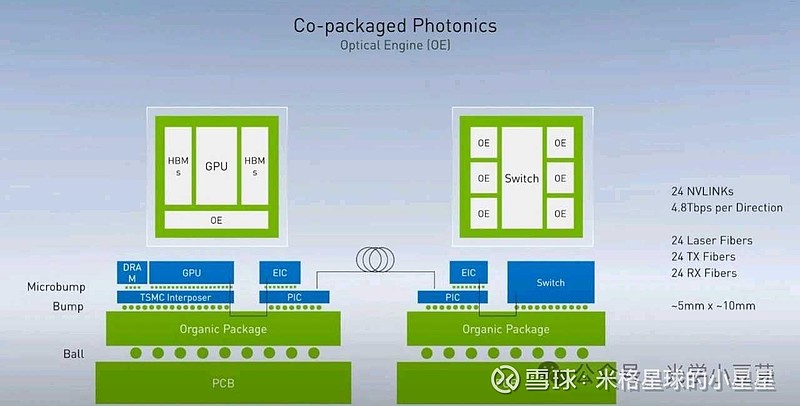

7. Nvidia

作为GPU领域的一哥,Nvidia也一直在布局硅光CPO技术。在2020GTC会议上,Nvidia展示过通过CPO实现GPU与Switch芯片互连的系统架构图。此外,Nvidia也与TSMC、Ayar Labs等公司合作,开发CPO技术。

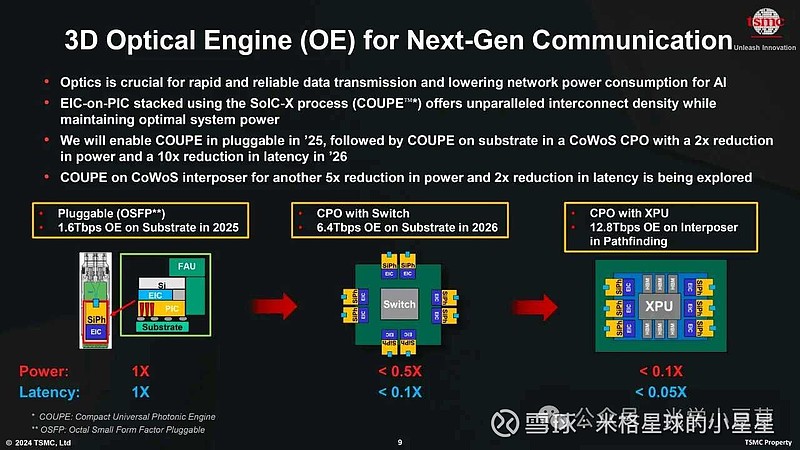

8. TSMC

台积电在2017年开始与Luxtera合作,开发了65nm节点的12寸硅光工艺平台,后续又引入先进封装,推出了COUPE 1.0/2.0平台(可以参看 TSMC硅光封装平台的最新进展)。TSMC最近发布了其在CPO领域的roadmap, 计划在2025年实现6.4Tbps的光引擎,后续进一步开发12.8Tbps光引擎,应用于XPU的互联。

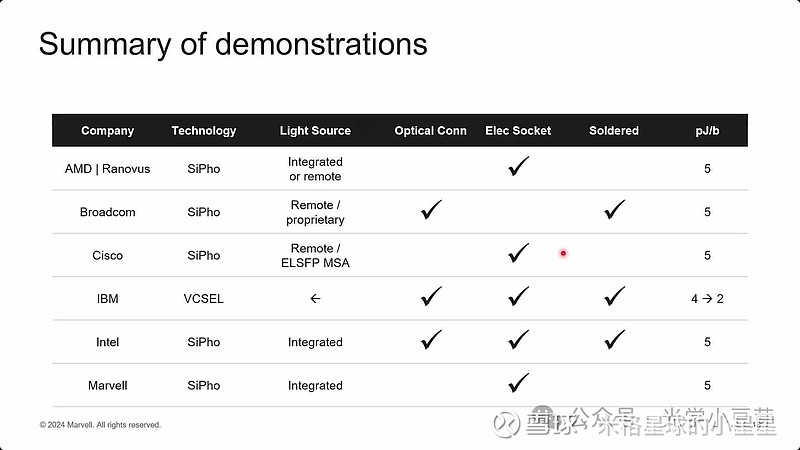

下表是对上述几家大厂CPO技术的整理。目前除了Broadcom之外,其它几家的方案并不是严格意义的CPO,而更像是NPO, 光引擎通过electrical socket与基板连接, 具备一定的可替换性。另外大部分厂家都选择了外置光源的方案,避免了内部大功率电芯片散热对激光器性能的影响。

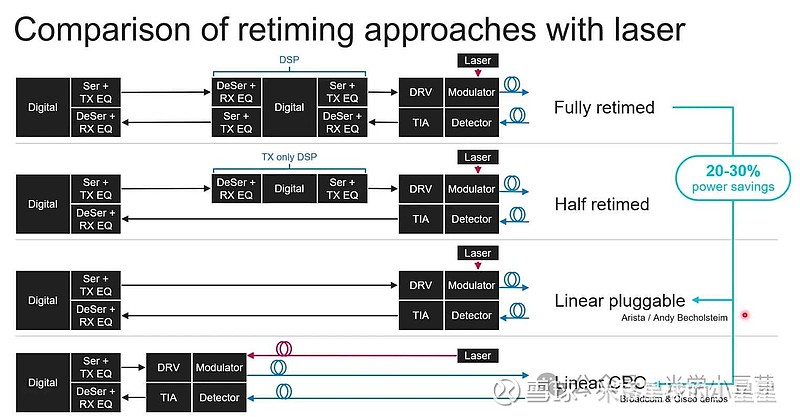

CPO技术的主要驱动力是其在能耗上的降低,由于光引擎距离ASIC芯片非常近,链路损耗降低,两者之间不需要retimer芯片对信号进行补偿,从而带来了其能耗约30%的降低。另外,CPO技术也提高了系统的带宽密度。

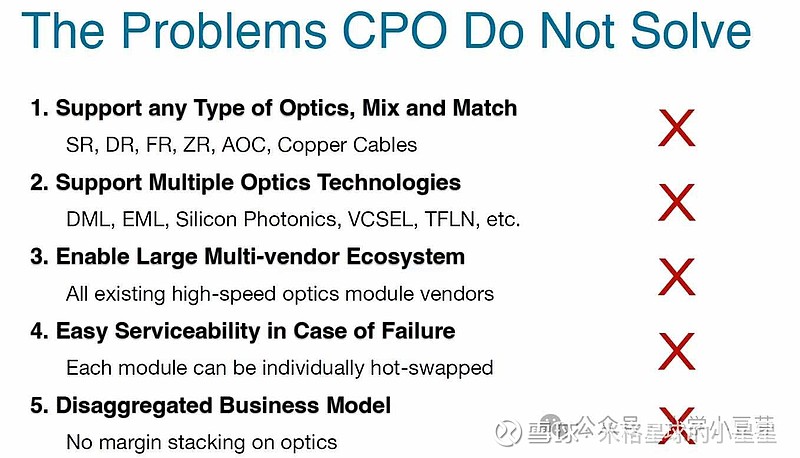

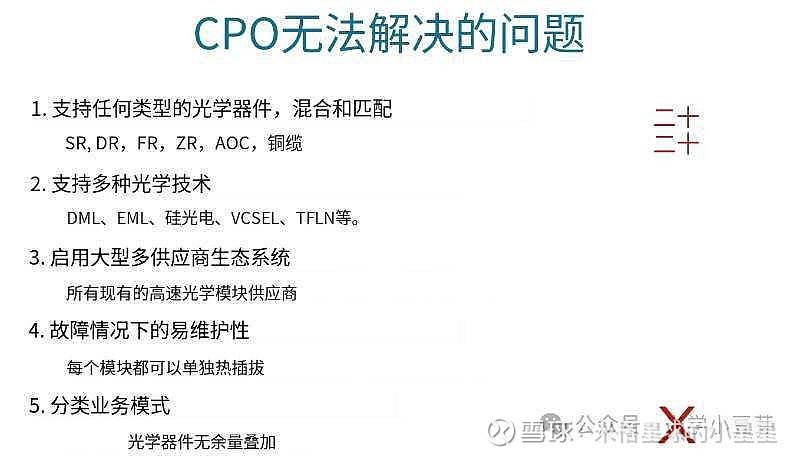

对CPO技术与商业模式的质疑,也一直存在。下图来自Arista的Andy大佬的ppt,相比于传统可插拔光模块,CPO技术的研发需要与Switch/XPU大厂深度合作,话语权在交换机厂商,对小公司不太友好。 另外, CPO模块在可靠性、可测试性、可替换性上一直被诟病,需要想办法解决这些问题。由于ASIC芯片与CPO光引擎封装在一起,ASIC芯片的价格十分昂贵,一旦CPO光引擎发生故障,如何快速的进行维修或替换?光电芯片合封在一起,也对系统散热带来了挑战。先进封装技术(TSV, FOWLP等)的引入,一方面带来了研发成本与开发周期的提高,另一方面也带来了良率的挑战。

CPO技术作为产业热点,得到了产业界的广泛关注,各家大厂也都在纷纷布局。它与可插拔光模块的争论,短期内还会持续下去。AI光互连的大背景下,对光模块可靠性的要求变得更为严格。虽然CPO技术在功耗和带宽密度上确实有优势,但是能否在商业上得到大规模应用,撼动可插拔光模块的地位,还有待商榷。相比较而言,Optical IO技术不会去瓜分可插拔光模块的蛋糕,可以解决传统电学IO在功耗、带宽等方面的难题,推广起来可能会更加顺利。

文章中如果有任何错误和不严谨之处,还望大家不吝指出,欢迎大家留言讨论。@起手一对A @悦然坐看云起 @顺势飞 @左庶子 @今晚不复盘 @在下不才极度厌蠢