芝能智芯出品

ASML宣布了推出新型光刻工具的计划,该工具旨在扩展芯片设计的极限,使晶体管密度达到一个新高度。

Part 1超越高数值孔径:引入Hyper-NA

ASML前总裁Martin van den Brink在imec ITF World会议上宣布了处于早期开发阶段的“Hyper-NA” EUV技术。

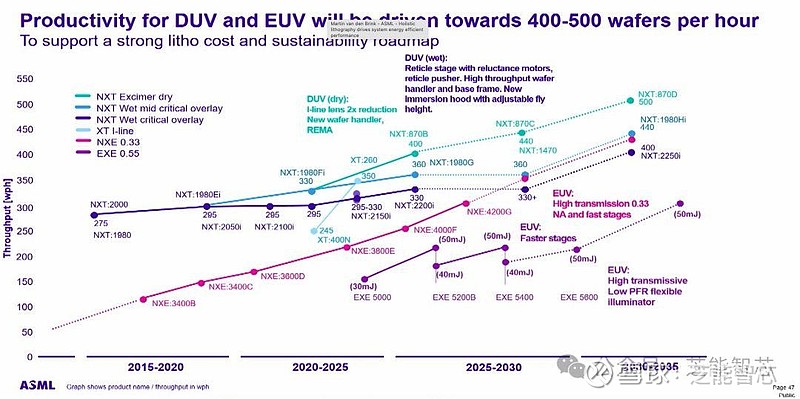

该技术将数值孔径(NA)从现有的0.55 NA提升至0.75 NA。这一宣布让业界专家们大吃一惊,并标志着ASML在高数值孔径(NA)系统之后,又一次迈向新的技术高峰。

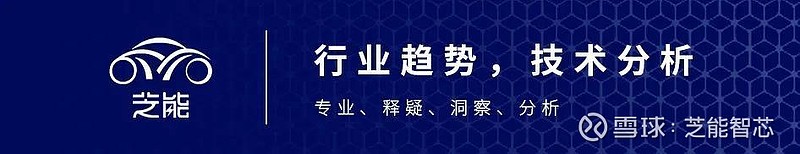

“从长远来看,我们需要改进我们的照明系统,我们必须采用Hyper-NA。与此同时,我们必须将所有系统的生产率提高到每小时400到500片晶圆。”

高数值孔径(High-NA)将早期EUV工具的0.33 NA提升至0.55 NA,帮助芯片制造商在未来十年内实现2纳米及更小的工艺节点。

根据van den Brink在imec活动上展示的图片,ASML计划在2030年左右推出超数值孔径(Hyper-NA),达到0.75 NA。这是马丁关于Hyper-NA的愿景,可行性研究目前正在进行中,这是ASML首次将Hyper-NA EUV添加到其路线图中。

Part 2面临的挑战

Hyper-NA面临着诸多技术挑战,其中之一是光的偏振问题。从0.55 NA开始,偏振问题变得显著,影响对比度。Ronse指出,需要偏振器来解决这一问题,但偏振器会阻挡光线、降低能效并增加生产成本。光刻胶的厚度在0.55 NA时已经变得极薄,而在超高NA情况下,这一问题将更加突出,给蚀刻选择性带来更大挑战。

今年4月,英特尔代工厂安装了首台高NA光刻系统。这一系统大幅提高了处理器的分辨率和功能扩展能力,使英特尔在18A工艺节点上保持领先。

然而,台积电目前还不计划安装高NA工具,而是利用其在双重图案化方面的专业知识与现有的EUV工具相结合。

其他使用EUV的领先芯片制造商,如三星、美光和SK海力士,也在考虑高NA技术。高NA预计将持续贯穿从2纳米到14埃、10埃甚至7埃的工艺节点,之后超NA将开始占据主导地位。

一旦高NA技术达到极限,Hyper-NA将成为唯一的替代方案。虽然纳米压印和多束电子束光刻技术曾被考虑作为替代方案,但其生产率和成本效益仍然不足。在光刻技术之外,研究人员正在探索新材料以缩小晶体管尺寸,但这种方法也面临物理极限。

未来,新的沉积工具和蚀刻技术将是关键,芯片的基础仍将是硅。

小结

ASML的Hyper-NA技术将推动芯片制造进入新的时代,随着技术不断进步行业创新将推动全球芯片制造的极限。