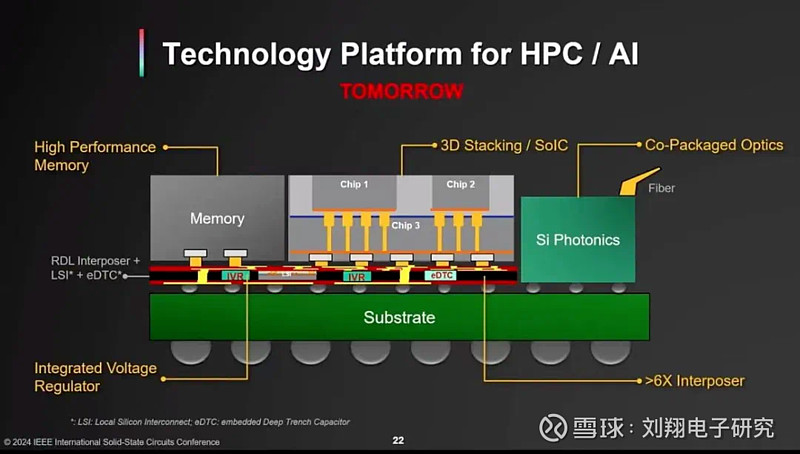

像上篇一样,开局一张图,如下:

这张图展示了以AI为代表的高端科技硬件未来趋势。能让全球各个科技巨头尿到一个壶里面去的,也是这张图。

原本两家都是晶圆制造巨头的海力士和台积电,已经开始在商谈合作了。上篇公众号《一图隐含未来十年生产力革命的硬机会(之一)》谈的就是为啥需要走到一起去?为啥HBM需求会很大?为啥难度很高?高在哪里?对哪些厂商有机会?

上篇谈完HBM,今天谈谈 3D Stacking。

英特尔CEO在上周提到:“五年前开发一款领先的 CPU,成本的15%将用于封装和测试。但到现在以Gaudi产品举例,封装和测试已占据35%到40%。”成本或者说说是价值量,为啥一下子就翻倍了呢?因为用到了3D Stacking技术。

3D 封装技术是一种先进的半导体封装技术,它将芯片堆叠在一起,以提高芯片的集成度和性能。3D 封装技术可以提高芯片的性能,降低芯片的尺寸和成本,提高芯片的可靠性和稳定性。

更具体来讲,先进封装的全部意义是什么? 答:1.实现更大的互连密度(每个区域有更多的互连);2.减少迹线长度(trace length )以降低每比特传输的延迟和能量。

以下是一些 3D 封装技术的运用:

三维堆叠封装(3D Stacking):通过将多个芯片堆叠在一起,实现更高的集成度和性能。

硅中介层封装(Silicon Interposer):使用硅中介层将多个芯片连接在一起,实现更高的带宽和更低的延迟。

封装内芯片互联(Chip-on-Wafer-on-Substrate):通过在封装内实现芯片互联,减少封装尺寸和成本。

封装内封装(Package-on-Package):通过将多个封装堆叠在一起,实现更高的集成度和性能。

封装内光学互联(Package-on-Package Optical Interconnect):通过在封装内实现光学互联,提高数据传输速度和带宽。

目前市场上主要的3D封装领导厂商有哪些家呢?有台积电、三星、英特尔等,以下是它们的 3D 封装技术的一些对比:

台积电:SoIC(System-on-Integrated Chips)和 InFO(Integrated Fan-Out)等。SoIC 可以将多个芯片堆叠在一起;InFO 是一种扇出封装技术,可以将芯片封装在一个小型封装中。

三星:X-Cube 和 HBM(High Bandwidth Memory)等。X-Cube可以将多个芯片堆叠在一起,实现更高的集成度和性能;HBM 是一种高带宽内存技术,可以实现更高的数据传输速度和带宽。

英特尔:Foveros 和 EMIB(Embedded Multi-Die Interconnect Bridge)等。Foveros 可以将多个芯片堆叠在一起;EMIB 是一种嵌入式多芯片互联桥接技术,实现更高的带宽和更低的延迟。

这些厂商,有哪些成功应用案例呢?

台积电已经成功将 SoIC 技术应用于苹果的 A14 芯片中,实现了更高的性能和更小的尺寸。

三星已经成功将 X-Cube 技术应用于自己的 Exynos 芯片中,实现了更高的性能和更小的尺寸。

英特尔已经成功将 Foveros 技术应用于自己的 LGA4189 处理器中,实现了更高的性能和更小的尺寸。

3D 封装技术的难点有哪些呢?

散热问题:由于芯片之间的距离很近,散热问题更加严重。

信号完整性问题:包括信号延迟、信号反射、信号衰减等,这些问题会影响芯片的性能和可靠性。

封装成本问题:需要使用先进的封装工艺和材料,因此封装成本较高;同时,需要解决芯片之间的连接问题,工艺流程负责,也会增加封装成本。

可靠性问题:包括芯片之间的热应力、机械应力等,这些问题会影响芯片的寿命和可靠性。

传统的封测流程包括磨片/背面减薄、切割、贴片、 银浆固化、引线焊接、塑封、切筋成型、FT 测试等环节。传统封装侧重于板级互联,先进封装侧重于晶圆级互联。

先进封装在晶圆上通过 TSV 和 RDL 分别实现纵向和横向的互联,而 TSV 和 RDL 则更类似于前道的晶圆制造工序,所以说先进封装是前道工序的衍生。

晶圆级封装的常见工艺流程包括:PI 光刻、溅射、PR 光刻、电镀、植球、磨片等。

PI 光刻 在 Wafer 表面涂覆 PSPI 光刻胶(Positive Photoresist),进行紫外线曝光,再通过显影和固化工艺,获得所需的 CD 开口位置。

溅射 通过物理气相沉积原理,将高纯度的金属材料置于真空室。通过离子束、电子束或高能粒子束来撞击金属材料表面,使其发生溅射,从而产生大量微小的金属颗粒。这些颗粒会沉积在晶圆表面上并形成金属薄膜。

PR 光刻 和 PI 光刻类似,区别在于曝光后无需固化,而是在电镀后进行去胶操作。

电镀 在种子层 UBM(Under Bump Metal)上方涂覆一层导电漆,用于芯片与外部电路板之间的连接。然后,将晶圆浸入含有铜离子的电解液中。将钎料作为阴极,使铜离子在钎料表面还原,形成一层均匀的铜层。电镀完成后,显影所预留的用于结构成型的光刻胶仍然处在晶圆表面,故需要使用药液喷淋的方式进行除胶。电镀后可能会出现的多余 UBM,通常需要使用腐蚀工艺去除。

植球 在焊盘位置涂覆助焊剂,在其对应位置放置锡球,利用 Reflow 将锡球焊接至焊盘位置。

磨片 将晶圆磨划至需求厚度,然后将处理完成的晶圆经过切割,分离 成单独的成品芯片。

硅通孔(TSV)是一种能让 2.5D/3D 封装遵循摩尔定律演进的互连技术。TSV 技术是 2.5D/3D 封装的关键技术。

TSV 技术的工艺流程包括:

1.晶圆的表面清洗、

2.光刻胶图案化、

3.干法/湿法蚀刻沟槽、

4.气相沉积、

5.通孔填充、

6.化学机械抛光等多道关键工艺。

TSV 工艺涉及的设备包括:

晶圆减薄机、

掩膜设备、

涂胶机、

激光打孔机、

电镀设备、

溅射台、

光刻机、

刻蚀机等。

晶圆厂、封测厂均对 TSV 技术有深度研究。台积电、三星、英特尔 等晶圆厂在前道制造环节经验丰富,对前道 TSV 技术熟能生巧,因而在 2.5D/3D 封装技术上独占鳌头。

考虑到先进封装在封装和测试行业中的重要性日益凸显,先进封装设备在封装和测试设备中的占比也有望进一步提升。国产先进封装设备厂商持续迭代新产品。

北方华创作为中国半导体设备龙头厂商之一,在先进封装领域亦有诸多布局。目前公司的 UBM/RDL 金属沉积设备、TSV 金属沉积设备、TSV 刻蚀设备、全新 DESCUM 设备已经正式投放市场或已经 完成研发。

芯源微作为中国半导体涂胶显影设备龙头厂商之一,在先进封装领域亦有诸多布局。目前公司的单 片湿法刻蚀设备、单片湿法去胶机、单片清洗机、涂胶显影设备已经正式投放市场。

盛美上海作为中国半导体清洗设备龙头厂商之一,在先进封装电镀设备和清洗设备领域亦有诸多布 局。目前公司已经成功开发先进封装电镀设备、3D TSV 电镀设备。多款设备也处于研发和量产前期。

由于公众号文章只能一天一发,我在知识星球上会有一些自己平时研究过程中发现以及市场上一些朋友的研究发现分享,内容会更丰富(昨天一天发了60条)、时效性也会更好。

发现雪球上不能分享二维码,我就给个知识星球的链接:网页链接