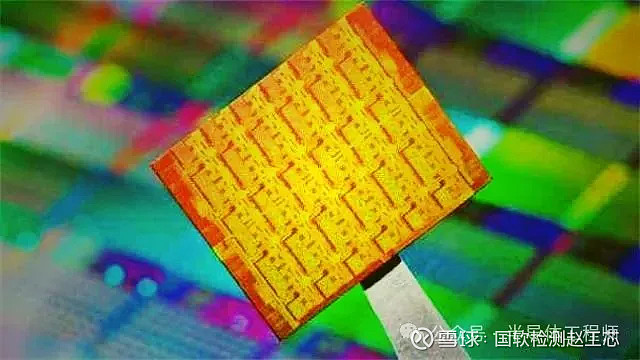

(资料图)

众所周知,晶圆和芯片的制造过程密切相关。晶圆是由单晶硅棒切割而成,而硅棒是圆柱形,所以将硅棒横截切得的就是圆形硅片。而硅片在光刻前,要用机器均匀涂抹光刻胶,通常的方式是甩胶。如果将晶圆切成方形,就会导致光刻胶涂抹不均匀,最后能用的范围还是中间的圆形。

除此之外,在硅片进行切角、打磨等过程的时候,硅片边缘也会积累不少的边缘应力,导致周围比较脆弱。如果将其做成方形的晶片,那么四角就会更加容易碎裂。所以,一直以来晶圆都要做成圆形的,而不是方形。

但现在,据上述媒体援引知情人士称,台积电为了应对人工智能带来的计算需求激增,正在探索使用510㎜ × 515㎜的矩形基板。由于矩形基板的有效面积比圆形晶圆大三倍多,边缘剩余的无效区域也更少。因此,这种设计不仅可以在每片基板上放置更多的芯片组,还有助于减少生产过程中的损耗,从而提高生产效率。

(相关报道截图)

据了解,台积电目前的先进芯片堆叠和组装技术,比如用于生产Nvidia、AMD、Amazon和Google的AI芯片,主要依赖于12英寸的硅晶圆,而这已经是现阶段可用的最大尺寸了。

但是,随着芯片尺寸的不断增大和市场对更多内存的集成需求,当前行业标准的12英寸晶圆或在几年内就将不足以满足尖端芯片的封装需求了。所以,许多业内人士都认为,未来封装的尺寸只会越来越大,以便从用于AI数据中心计算的芯片中挤出更多的计算能力。

然而,台积电探索的这种“矩形代替圆形晶圆”的封装方法,实现起来并不容易。该媒体指出,目前这项研究仍然处于早期阶段,可能需要“几年”才能商业化,因为在新形状基板上的尖端芯片封装中涂覆光刻胶,是这项研究中的一个关键瓶颈。这要求台积电这样的芯片制造巨头发挥其深厚的财力优势,推动设备制造商进行设备设计的革新。

如果上述消息属实,它将标志着台积电在芯片封装技术上的重要转变。

来源于21ic电子网,作者蔡璐整理

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。203篇原创内容公众号

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。203篇原创内容公众号