芝能智芯出品

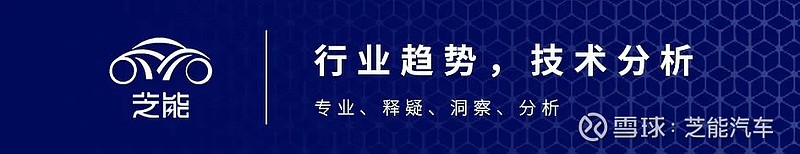

三星代工厂在本周的美国三星代工论坛 (SFF) 上公布了其最新的工艺技术路线图,涵盖了从2nm级生产节点到2027年的演进计划。

此次公布的路线图不仅包含了背面供电(BSPDN)技术的应用,还强调了在2027年推出1.4nm级节点的计划,以及引入“高价值”的4nm级制造技术。

Part 1

2nm级工艺技术:未来的核心

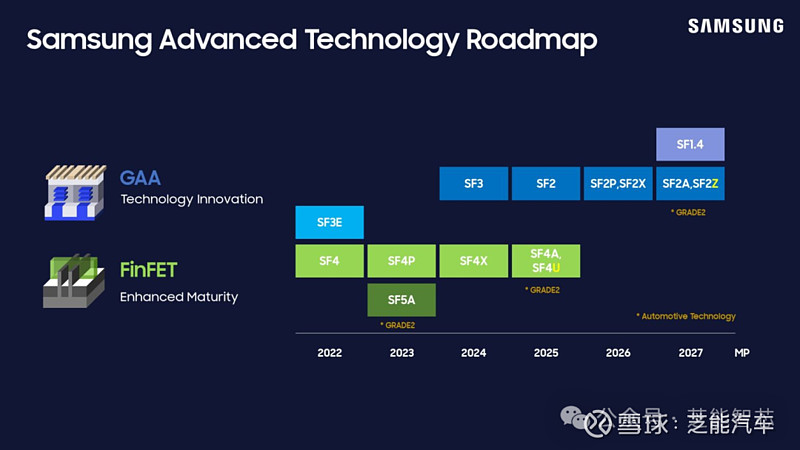

三星在此次论坛上发布了两个新的尖端工艺节点——SF2Z 和 SF4U,以进一步强化其领先的工艺技术路线图。

●SF2Z:该2nm工艺节点采用优化的背面供电网络 (BSPDN) 技术,将电源轨置于晶圆背面,从而消除电源线和信号线之间的瓶颈。与第一代2nm节点SF2相比,SF2Z在功率、性能和面积 (PPA) 上都有显著改进,并且显著降低了电压降 (IR降)。SF2Z预计将在2027年实现量产。

●SF4U:作为一种高价值的4nm变体,通过结合光学缩小来提供PPA改进,计划于2025年实现量产。

三星重申,SF1.4(1.4纳米)的准备工作进展顺利,性能和良率目标有望在2027年实现量产。公司强调其对超越摩尔定律的持续承诺,通过材料和结构创新,积极塑造1.4纳米以下的未来工艺技术。

三星重点集中在2nm级工艺技术上,预计将在2025年投入生产,并持续发展至2027年,届时1.4nm级生产节点也将投入使用。

为了进一步优化性能,三星将此前披露的SF3P节点重新命名为SF2,并进行了多项改进,带来了显著的功率、性能和面积 (PPA) 优势。三星对SF3P进行了改进,形成了现在的SF2。这个增强节点采用了各种工艺设计改进,带来了显著的PPA优势。

●新节点的推出计划

除了2nm级工艺技术,三星还公布了未来几年的节点演进计划:

◎2026年:推出SF2P,这是对SF2的进一步改进,采用了速度更快但密度较低的晶体管。

◎2027年:推出SF2Z,增加了背面供电技术,以实现更好、更高质量的供电,特别是针对芯片设计中的电压降问题。

◎1.4nm级节点SF1.4:预计在2027年问世,但目前没有采用背面供电技术。根据目前的路线图,三星将成为唯一一家在其首个1.4nm节点中未使用BSPDN的代工厂。

Part 2

AI时代的技术优势与挑战

在AI时代,结构性改进如环栅 (GAA) 技术已成为满足功率和性能需求的必要条件。

三星在SFF上强调了其GAA技术的成熟度,并展示了其在良率和性能方面的持续提升。

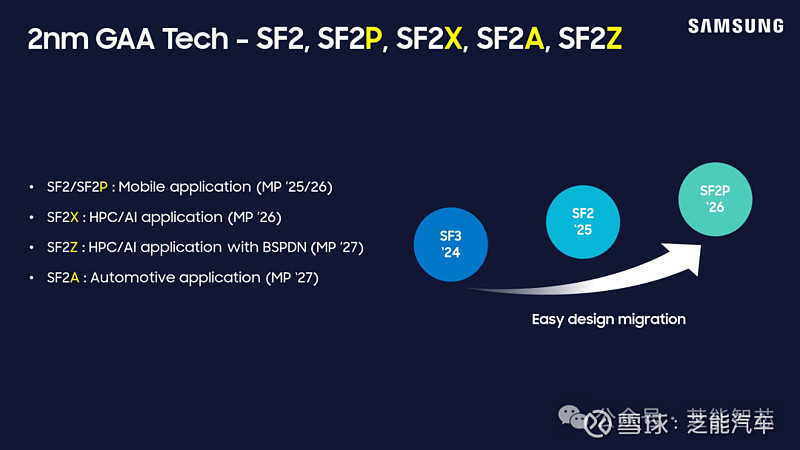

三星计划在今年下半年量产其第二代3nm工艺 (SF3),并在即将推出的2nm工艺上实现GAA技术的应用。三星推出了集成三星AI解决方案平台,这是公司代工、内存和高级封装(AVP)业务部门共同努力的成果。

通过整合各业务的独特优势,三星提供高性能、低功耗和高带宽的解决方案,并可根据客户的特定AI需求进行定制。跨公司协作简化了供应链管理 (SCM) 并缩短了产品上市时间,使总周转时间 (TAT) 显著提高了20%。

三星计划在2027年推出一体化、共封装光学 (CPO) 集成的AI解决方案。

三星强调了背面供电技术的优势,并计划首次将其纳入SF2Z节点。背面供电技术有助于优化电力输送,减少电压降,从而提高芯片的整体性能和效率。三星目前尚未具体透露SF2相对于SF3P的详细PPA改进。

与其他芯片代工的路线图相比,三星在“纳米”指定方面与其他代工厂大致一致。具体技术细节和实际性能优势尚未完全披露,使得三星与英特尔和台积电的技术对比仍有待进一步观察。

英特尔和台积电同样在积极推进其战略目标尖端节点的开发。英特尔计划在2024年推出Intel 20A节点,并逐步推进至2027年的Intel 10A节点。台积电则计划在2024年推出N3E和N3P节点,并在2026年和2027年分别推出A16和A14节点。

小结

三星最新的工艺技术路线图展示了其在2nm及以下节点上的持续创新和发展。随着BSPDN技术的引入和1.4nm节点的推出,三星致力于在半导体制造领域保持领先地位。

随着竞争对手同样积极推进其技术进步,三星面临的挑战依然巨大。未来几年,半导体行业的技术演进将持续引领科技的发展方向,三星的每一步动向都将备受关注。