芝能智芯出品

在IMAPS DPC 2024上,Yole的两位分析师 Rayane Mazari & Gabriela Pereira对智能手机SoC做一些分析,分享如下。

随着智能手机市场的不断增长,对于高性能、低功耗的移动应用处理器(APU)的需求日益增加。

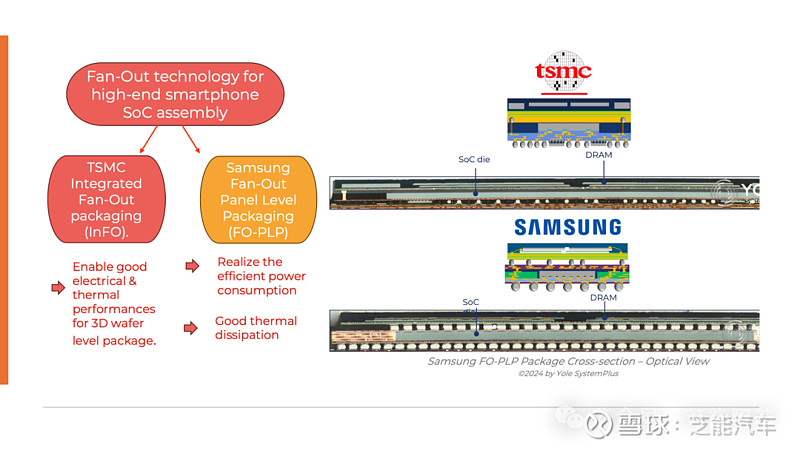

在这种背景下,扇出技术(Fan-Out)作为一种先进的封装技术,正在逐渐成为智能手机SoC封装的主流选择。本文主要围绕扇出技术在智能手机APU封装中的应用,以及其对未来智能手机设计的影响。

Part 1

智能手机APU市场概览

根据Yole Group的数据,智能手机APU市场在接下来的几年内预计将保持稳定。高通(Qualcomm)、苹果(Apple)和联发科(MediaTek)是主要的智能手机APU设计公司。

虽然智能手机市场整体增长放缓,但高端智能手机市场对于高性能APU的需求依然强劲。

●什么是扇出技术(Fan-Out)?

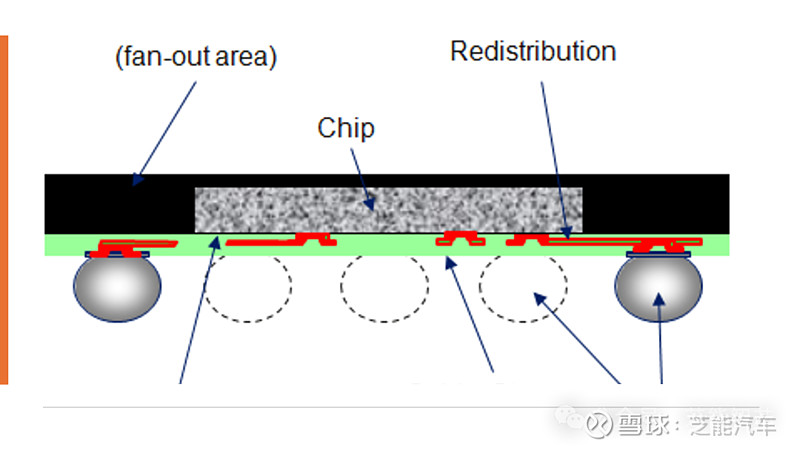

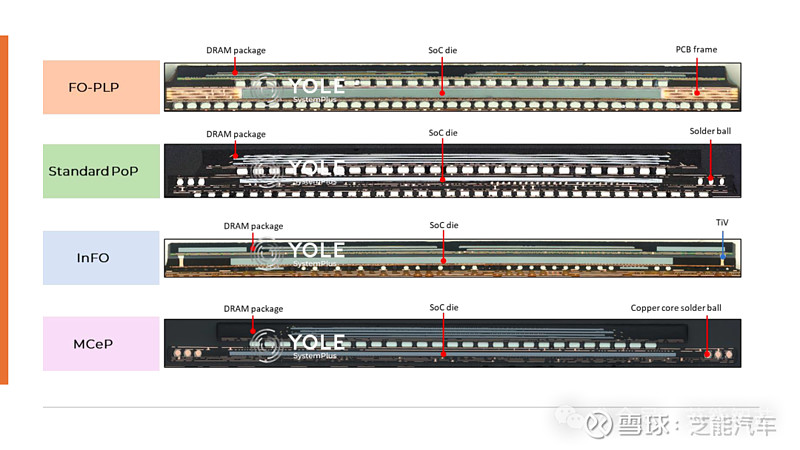

扇出技术是一种先进的封装技术,能允许在晶圆级封装之外的区域形成额外的I/O(输入/输出)点,从而提高芯片的性能和功能。与传统的晶圆级封装相比,扇出技术提供了更好的电气和热性能,同时还能实现更小的封装尺寸。

●扇出技术在高端智能手机中的应用

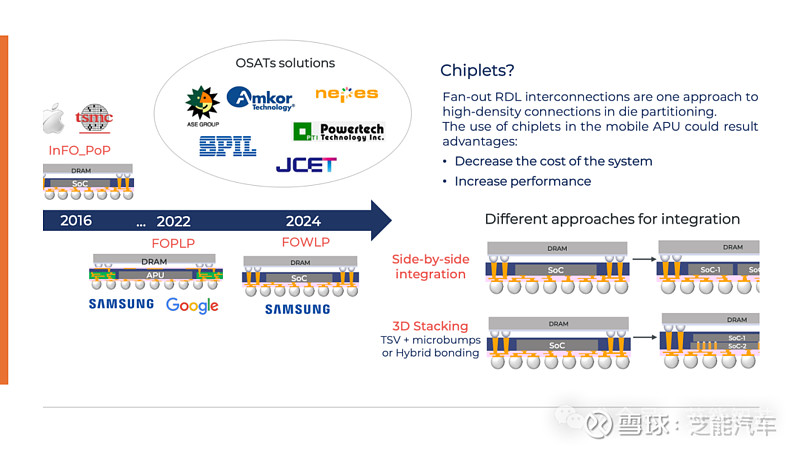

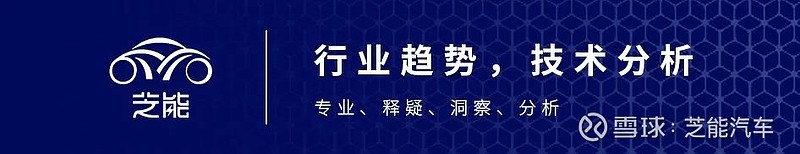

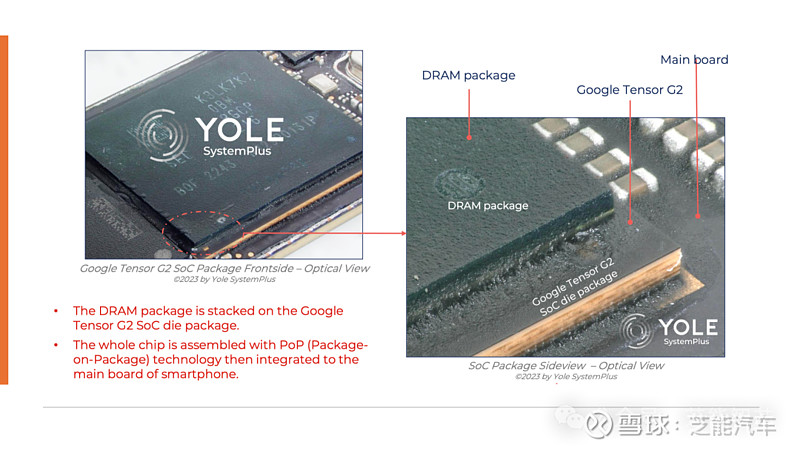

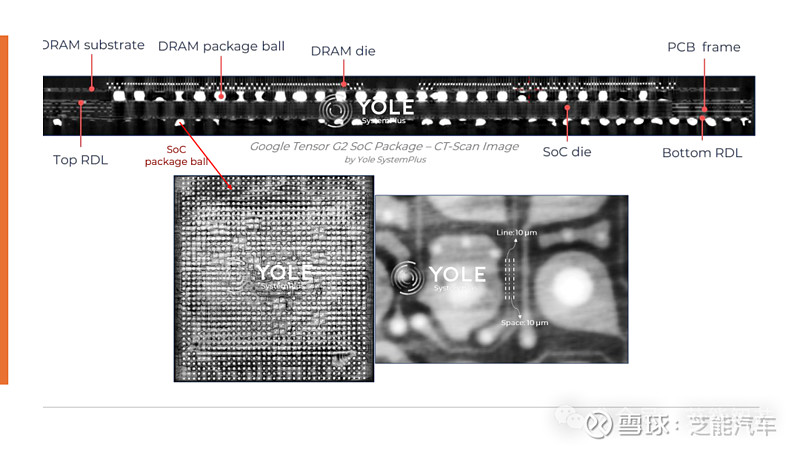

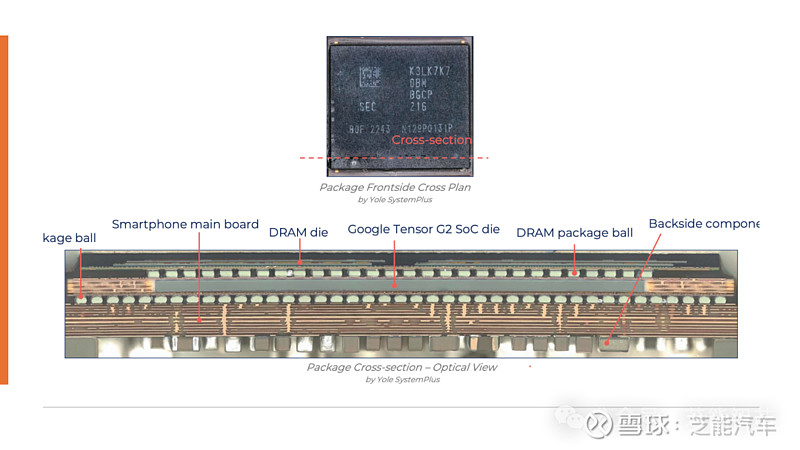

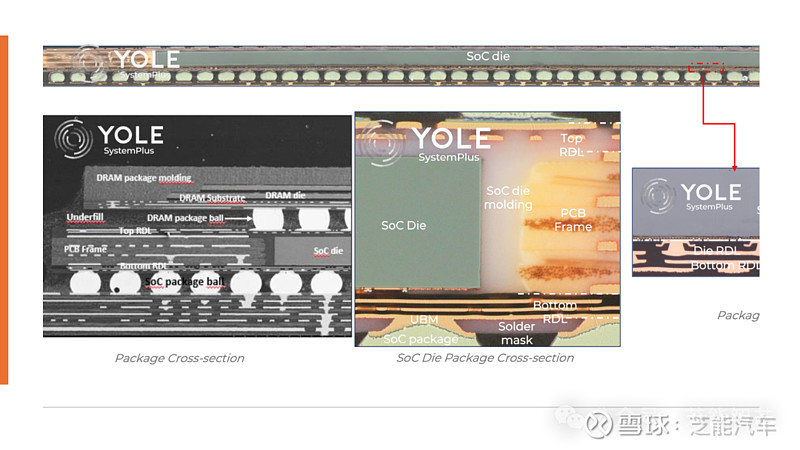

三星(Samsung)和台积电(TSMC)是扇出技术的领先供应商。例如,谷歌Pixel 7 Pro智能手机使用的Google Tensor G2 SoC就是采用三星的扇出技术进行封装的。

这种封装方式不仅提高了SoC的功率效率和热散性能,还使得整个芯片能够通过PoP(Package on Package)技术与DRAM封装堆叠,进而集成到智能手机的主板上。

Part 2

扇出技术的成本分析

市场和未来发展

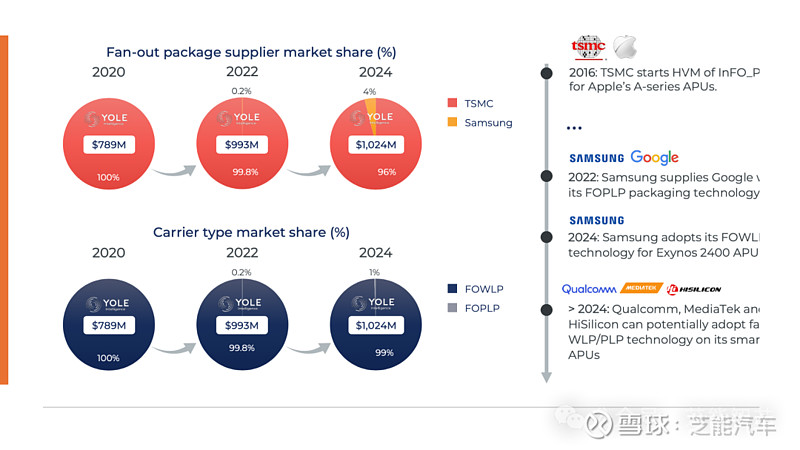

扇出技术带来了性能上的提升,但其成本问题仍然是一个关键考量。根据Yole Group的分析,扇出封装的成本正在逐渐降低,预计到2028年,扇出封装的平均售价(ASP)将与其他类型的封装相竞争。扇出技术的市场正在快速增长。

TSMC和三星是扇出封装市场的主要供应商,并且预计到2024年,高通、联发科和海思可能会在其智能手机APU上采用扇出WLP(Wafer Level Package)/PLP(Panel Level Package)技术。

扇出技术的未来发展方向包括使用更多的RDL(再分布层)以提供更高的互连密度,以及通过芯片分割和使用芯片组(Chiplets)来降低系统成本并提高性能。

不同的集成方法,如并排集成、3D堆叠、TSV(Through-Silicon Vias)和混合键合技术,也将推动扇出技术的发展。

小结

扇出技术正在成为高端智能手机SoC封装的关键技术,它不仅提高了智能手机的性能,还为未来的封装技术发展提供了新的方向。

随着成本的降低和技术的成熟,我们可以预见,扇出技术将在未来的智能手机设计中扮演越来越重要的角色。