$天岳先进(SH688234)$ $三安光电(SH600703)$ $斯达半导(SH603290)$ #第三代半导体#

04 碳化硅的产业链 - 器件

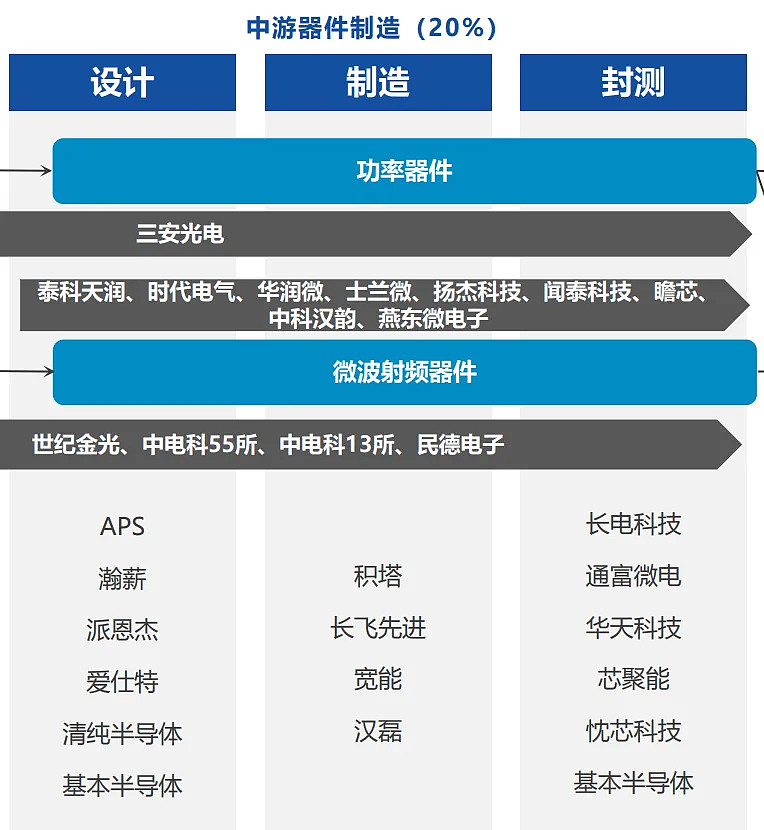

本篇主要聊聊碳化硅器件,这里又包括设计、制造、封测三大环节。

01 设计

对于碳化硅器件来说,高质量的衬底可以从外部购买得到,高质量的外延片也可以从外部购买到(衬底与外延,后续大规模稳定量产后会逐渐成熟,且成本下降会很快),可是这只是具备了获得一个碳化硅器件的良好基础,高性能的碳化硅器件对于器件的设计和制造工艺有着极高的要求,而设计(类似于芯片设计)往往是最具有决定性作用的。

功率MOSFET为电压型控制器件,驱动电路简单,驱动的功率小,而且开关速度快,具有高的工作频率。

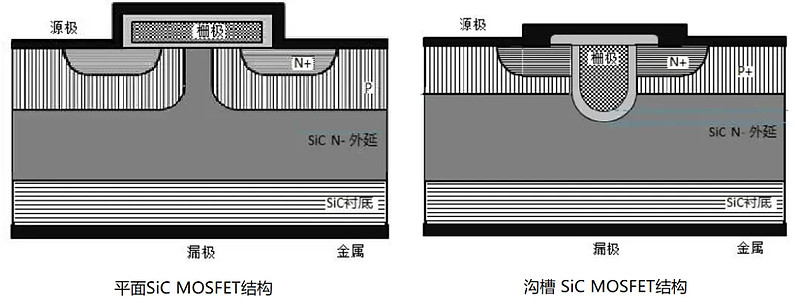

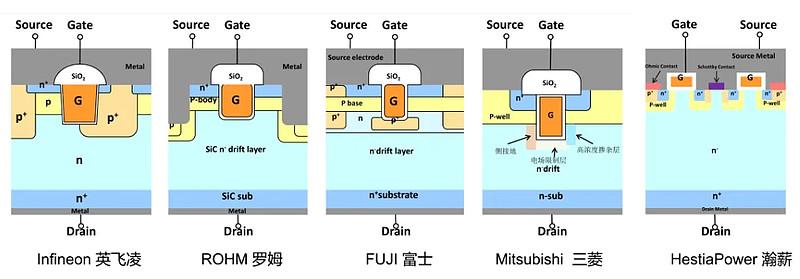

目前,SiC行业出现了两极分化:一方面是选择保守、安全的平面MOSFET设计,另一方面是大力发展高效、紧凑的沟槽MOSFET设计。

直到2023年底,西方SiC器件制造商“五巨头”之间一直存在分歧,意法半导体、安森美和Wolfspeed一直在追求传统的“平面”MOSFET架构,而罗姆和英飞凌则在开发更复杂的沟槽 MOSFET架构。

平面结构的特点就是工艺简单,单元一致性较好,雪崩能量比较高。但是,这种结构容易产生JFET效应,增加通态电阻,寄生电容也较大。

- 意法半导体主要以平面结构为主,推出了第4代平面栅碳化硅,并在今年第二季度量产;相比上一代产品,第4代平面栅碳化硅的性能有所进步,包括导通电阻减少15%,工作频率增加一倍至1MHz。

- Wolfspeed碳化硅MOSFET采用平面设计,目前处于第3代(Gen 3),涵盖650V到1200V之间的多个电压规格。Gen 3平面MOSFET采用六边形晶胞微观设计,650V Gen 3和1200V Gen 3+的单位面积导通电阻分别为2.3 mΩ·cm2和2.7 mΩ·cm2,较上一代Strip Cell减少了16%。Gen 4沟槽栅还在开发中,具体量产时间还没有透露。

沟槽结构则将栅极埋入基体中,形成垂直的沟道,由于要开沟槽,工艺变得复杂,单元一致性、雪崩能量比平面结构要差。不过,这种结构没有JFET效应,具有更高的沟道密度,同时沟道所在SiC晶面具有较高的沟道迁移率,导通电阻比平面结构明显降低;同时,寄生电容更小,开关速度快,开关损耗非常低。但是,也存在比较明显的问题:由于器件工作在高压状态,内部工作电场强度高,尤其是沟槽底部,工作电场强度非常高,很容易在局部超过最大的临界电场强度,从而产生局部的击穿,影响器件工作的可靠性。

- 英飞凌CoolSiC™ MOSFET采用了不对称的沟槽结构,该结构中MOS沟道选择了最有利的方向。

- ROHM公司已经开发出了第三代产品 - 双沟槽MOSFET结构,该结构同时具有源极沟槽和栅极沟槽。

总结而言,从性能上看,平面肯定不如沟槽,但平面结构还是具备可靠性的优势,目前沟槽还面临着制造工艺难度大的问题。但是,未来沟槽的技术演进也是在不断地解决这一问题,而且越来越多的厂家将研发方向放在沟槽,这其中主要是要解决可靠性的问题,落到实际层面其实就是“如何减小沟槽底部的工作电场强度”。

02 制造

碳化硅器件制造环节与硅基器件的制造工艺流程大体类似,主要包括“光刻、清洗、掺杂、蚀刻、成膜、减薄”等工艺。

碳化硅材料的特殊性质决定其器件制造中某些工艺需要依靠特定设备进行特殊开发,以促使碳化硅器件耐高压、大电流功能的实现,主要涵盖“掺杂、栅结构成型、形貌刻蚀、金属化、减薄工艺”。

❶ 注入掺杂与退火

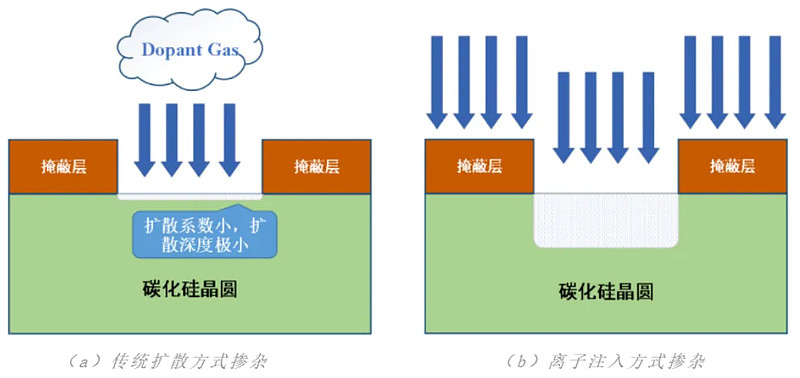

在掺杂步骤中,传统的硅功率器件工艺中,高温扩散和离子注入是最主要的掺杂控制方法,两者各有优缺点,这里就不赘述。

而在碳化硅功率器件掺杂工艺中,常用的掺杂元素有:N型掺杂,主要为氮元素和磷元素;P型掺杂,主要为铝元素和硼元素。掺杂元素在硅中的扩散系数较高,所以在1300℃左右就可以实现高温扩散掺杂。与硅中扩散系数相比,磷、铝、硼和氮元素在碳化硅中的扩散系数都很低,因此碳化硅中需要2000℃以上的温度才能得到合理的扩散系数。

但是,高温扩散会带来很多问题,如引入多种扩散缺陷会恶化器件的电学性能,无法使用常见的光刻胶作掩膜等等,所以离子注入工艺成为了碳化硅掺杂的唯一选择。

而高温离子注入后,碳化硅材料原本的晶格结构被破坏而变成非晶态,这种晶格损伤必须在退火过程中修复成单晶结构并激活掺杂物。

在高温退火过程中,原子可以从热能中获得能量并进行快速热运动。当运动到单晶晶格位置中具有最低自由能,它就会停留在此位置。所以被破坏的非晶态中的碳化硅与掺杂原子,将在靠近衬底界面位置,通过落入晶格位置并且被晶格能束缚后完成了单晶结构构建。这样晶格修复和提高激活率是在退火过程中同时完成的。退火温度如果是1400℃,激活率小于10%;一般需要高达1600℃,才能达到90%的激活率。

离子注入和激活退火的工艺难度很高,不可避免地还会产生降低器件性能的各种缺陷。因此,控制缺陷、提升良率的要求无疑对设备和工艺控制都带来了极大的挑战。

因此,是否具备高温高能离子注入机已经成为衡量碳化硅生产线的重要标准之一。

目前,高温高能离子注入机主要还是由美国厂商垄断,美国应用材料公司和美国Axcelis公司合计占据了全球70%以上的市场。据悉,烁科中科信是目前国内唯一能提供此设备的公司,国产化率100%,稳居国内市场占有率第一。而在高温退火炉方面,国外主要厂商主要包括Centrotherm、日本真空等;国内涉及得厂商包括北方华创、中国电科48所、屹唐半导体等。

❷ 栅结构成型

SiC/SiO2界面质量对MOSFET沟道迁移和栅极可靠性影响很大,需要开发特定的栅氧及氧化后退火工艺,以特殊原子(例如氮原子)补偿SiC/SiO2界面处的悬挂键,满足高质量SiC/SiO2界面以及器件高迁移的性能需求。核心工艺为栅氧高温氧化、LPCVD、PECVD。

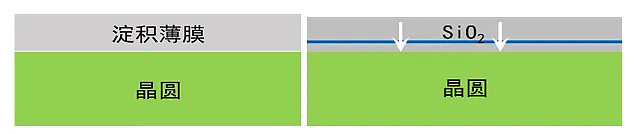

普通氧化膜淀积和高温氧化示意图

❸ 形貌刻蚀

碳化硅材料在化学溶剂中呈现惰性,精确的形貌控制只有通过干法刻蚀方法实现;掩膜材料、掩膜蚀刻的选择、混合气体、侧壁的控制、蚀刻速率、侧壁粗糙度等都需要根据碳化硅材料特性开发。核心工艺为薄膜沉积、光刻、介质膜腐蚀、干法刻蚀工艺。

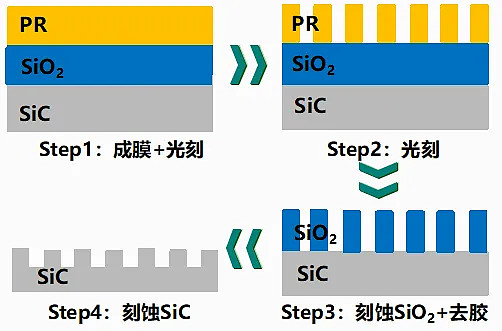

碳化硅刻蚀过程示意图

❹ 金属化

器件的源电极需要金属与碳化硅形成良好的低电阻欧姆接触。这不仅需要调控金属淀积工艺,控制金属-半导体接触的界面状态,还需采用高温退火的方式降低肖特基势垒高度,实现金属-碳化硅欧姆接触。核心工艺是金属磁控溅射、电子束蒸发、快速热退火。

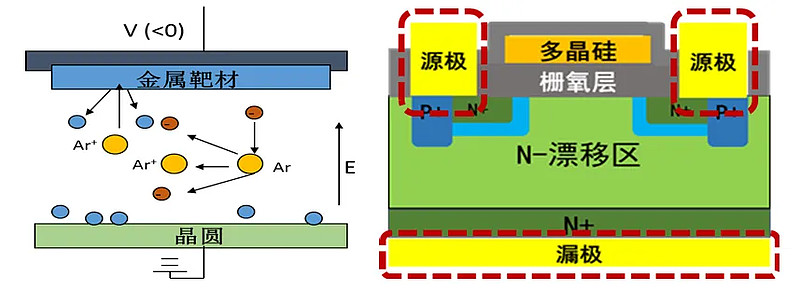

磁控溅射原理和金属化效果示意图

❺ 减薄工艺

碳化硅材料具有高硬度、高脆性和低断裂韧性的特点,其研磨加工过程中易引起材料的脆性断裂,对晶圆表面与亚表面造成损伤,需要新开发研磨工艺来满足碳化硅器件制造需求。核心工艺是磨片减薄、贴膜揭膜等。

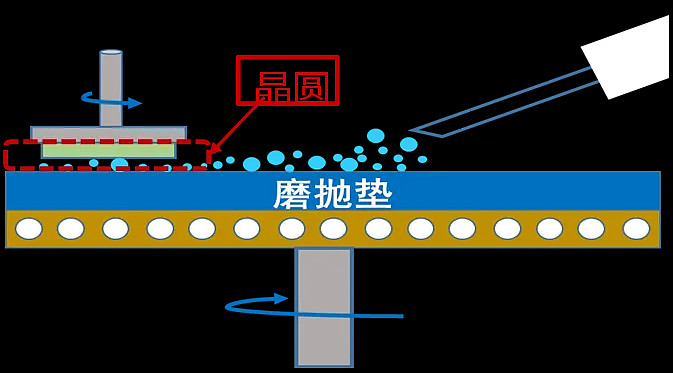

晶圆磨抛/减薄原理示意图

03 封测

碳化硅芯片的优良特性,需要通过封装与电路系统实现功率的高效、高可靠连接,才能得到完美展现。

目前新的设计SiC模块的设计方向是结构紧凑更紧凑,通过采用双面银烧结和铜线键合技术,以及氮化硅高性能AMB陶瓷板、用于液冷型铜基PinFin板、多信号监控的感应端子(焊接、压接兼容)设计,努力往低损耗、高阻断电压、低导通电阻、高电流密度、高可靠性等方向努力。

目前,碳化硅功率模块封装创新主要朝着如下几个方向在走:

- 更先进的连接材料以及连接工艺,以承受更高的温度变化

AI2O3-DBC热阻最高,但是制造成本最低;AlN-DBC热阻最低,但韧性不好;Si4N3-AMB陶瓷材料热阻居中,韧性极好,热容参数也更出色,可靠性远超AlN和AI2O3,使得模块散热能力、电流能力、功率密度均能大幅提升,其与第三代半导体衬底SiC晶体材料的热膨胀系数更为接近,匹配更稳定非常适合汽车级的碳化硅模块应用。AMB陶瓷基板有望成为IGBT和SiC器件领域新趋势。

- 更短的连接路径以及更先进的连接技术,以降低杂感来适应器件高频特性

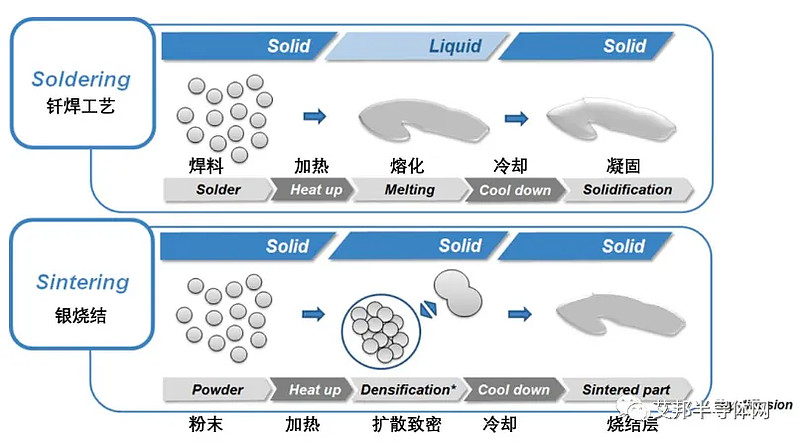

银烧结是目前碳化硅模块领域最先进的焊接技术,可充分满足汽车级功率模块对高、低温使用场景的严苛要求。相较于传统锡焊技术,银烧结可实现零空洞,低温烧结高温服役,焊接层厚度减少60-70%,适合高温器件互连,电性能、热性能均优于锡焊料,电导率提高5-6倍,热导率提高3-4倍。

- 更集成的封装结构设计以及电路拓扑,以进行更好的系统热管理

为使模块产品热路径设计更紧凑,促使逆变器系统集成设计更紧凑高效,进一步降低整体系统逆变器成本,通过封装形式的改变,改善散热性以及通流能力。采用多芯片并联的内部结构,各并联主回路和驱动回路参数基本一致,最大程度保证并联芯片的均流性。模块内部封装有温度传感器(PTC),且PTC安装在靠近芯片的模块中心位置,得到了一个紧密的热耦合,可方便精确地对模块温度进行测量。

本篇能成文主要还是参考了以下公众号及资料,自我学习的过程,以下一并感谢:功率半导体之家、碳化硅研习社、NE时代半导体、智慧半导体、浩高电子科技、艾邦半导体网等。

未完待续,敬请关注。

VC金水河 | 新材料产业投资 | 央企产业基金合伙人

版权声明:

本公众号是以个人原创与知识分享为宗旨的学习与交流平台,部分内容为原创,其它内容来自于网络或公众号转载。我对文中观点即使表示赞同,也无法对其内容的准确性、可靠性或者完整性提供任何明示或暗示的保证,请仅作学习参考。我非常尊重作者的成果与奉献,如有侵权,请联系我及时删除。