在数字化时代,数据的力量日益凸显,人工智能(AI)和高性能计算(HPC)作为现代科技的双引擎,正推动着全球高带宽存储芯片(HBM)市场的蓬勃发展。过去的一年各大芯片巨头竞争台积电先进封装产能,而HBM作为GPU的最强辅助,能够满足其对于内存带宽和容量的高需求。近期HBM三大原厂相继宣布扩产计划,以应对全球对高性能存储解决方案的迫切需求。根据高盛的预测,从2023年到2026年,HBM市场将以年复合增长率约100%的速度增长,届时市场规模有望达到250亿美元。

什么是HBM

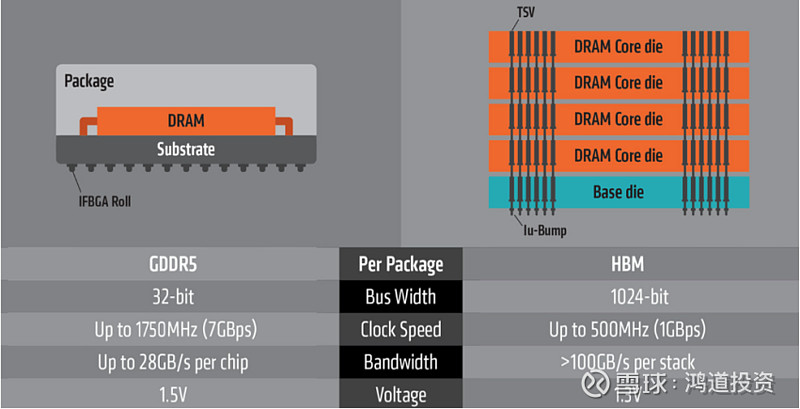

HBM(High Bandwidth Memory)高带宽存储器,作为动态随机存取存储器(DRAM)的一种,虽然与LPDDR,DDR,GDDR这些主要大类使用相同的DRAM存储单元(DRAM Die),但因其独特的架构功能,常被运用于高性能计算(HPC),网络交换及转发设备等需要极高吞吐量的数据密集型领域。

(资料来源:AMD官网、国金电子)

传统GDDR因采用基于冯·洛伊曼理论即存算分离的系统架构一直存在“内存墙”的问题——存储与计算单元分离,存储器与处理器之间通过总线传输数据,会产生以下三方面问题:

(1)存储带宽问题:由于CPU和存储器采用的制造工艺存在差异,CPU通常采用速度更快的SRAM寄存器,具备双稳态特性,而存储器则倾向于使用速度相对较慢的DRAM寄存器,具有单稳态特性。这种工艺上的差异导致了两者性能的巨大差距。在过去的20年中,CPU的处理能力增长了惊人的90000倍,而存储器的带宽仅提升了30倍。存储带宽的限制通过总线对计算单元的带宽产生了制约。这种数据传输速度的巨大差距使得传统DRAM难以满足AI训练所需的巨大计算需求。

(2)传输效能问题:由于数据存储和计算单元之间的物理分离,导致数据传输过程中出现显著的延迟,这使得计算后的数据大部分时间都花费在从存储器中读取数据上。这种I/O延迟不仅影响了用户体验,而且数据传输过程中的能量消耗占据了总计算能量的60%到90%,造成了严重的效能浪费。

(3)占用空间问题:传统的GDDR技术由于其2D平面布局,占用的空间较大,这与当前消费电子产品追求的轻薄化和便携化趋势不相符。随着技术的发展,市场对更紧凑、更高效的存储解决方案的需求日益增长。因此HBM相较于传统DRAM具有更高速,更低耗,更轻薄等优点。

HBM的竞争格局

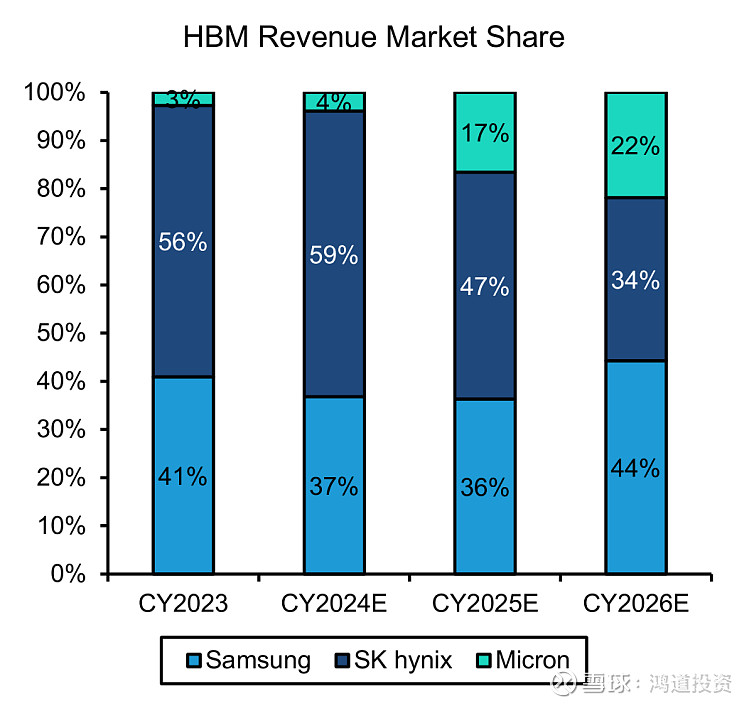

在HBM市场的竞争中,SK海力士、三星和美光三大厂商各占鳌头。SK海力士凭借其先发优势,在市场上占据了较大的份额。三星作为老牌的存储原厂,前期忽视了HBM的爆发性,导致在新一代产品布局有所落后,随着产能功耗的问题逐步解决,三星也将拿回属于自己的份额。此外美光为了追赶海力士的步伐跳过了HBM3的研发,从HBM2e直接到HBM3e,这也导致了在当前HBM3主流的市场中,美光目前仅有5%不到的市场份额。然而随着美光积极在台湾和日本扩产以及HBM3e在GPU的占比提升,管理层也表示未来要HBM的市场份额要做到跟自己DRAM一样(25%)的水平。

(资料来源:Trendforce、Bernstein estimate)

各大厂商在HBM技术和产能方面都取得了显著的进展。SK海力士开发出了全球首款12层堆叠的HBM3 DRAM,并已向客户提供样品,计划在今年上半年完成新产品的量产准备。三星则已经开始向客户提供9.8Gbps速率的HBM3E内存样品,并预计在2025年推出HBM4内存。美光最近开始量产其HBM3E内存,该产品具备8层堆叠和24GB容量,具有1024位接口、9.2GT/s的数据传输速率和1.2TB/s的带宽。

HBM未来期待与挑战

HBM 4的推出预计将带来性能上的显著提升,带宽接近1TB/秒,这将为高性能计算和AI领域带来革命性的变化。HBM4将采用混合键合技术,无需在DRAM内存层间添加凸块,而是将上下两层直接铜对铜连接,这显著提高了内存的集成度和效率。这种技术的应用进一步优化了空间利用率,使得内存堆叠更加紧凑和高效。但同时随着堆叠到16层,散热将成为主要问题,也是未来HBM“御三家”主要的竞争方向。

随着技术的不断进步和市场需求的增加,HBM市场的竞争将变得更加激烈。这不仅为各大厂商带来了挑战,也为整个行业的发展带来了无限的机遇。我们有理由相信,在未来几年内,HBM市场将继续保持其快速增长的势头,为全球的科技发展贡献重要的力量。同时,随着技术的成熟和成本的降低,HBM技术有望在更广泛的应用场景中发挥其潜力。

苹果WWDC2024-端侧AI的曙光已经升起

自动驾驶法规逐步完善,自主车企借东风发力

理想与现实 - Infiniband和以太网的抉择