在半导体测试领域,JTAG(Joint Test Action Group)已经成为不可或缺的一部分。本文将带您深入了解JTAG的概念、架构、指令集及其在边界扫描测试中的应用,帮助您更好地掌握这一重要技术。

一、JTAG的概念

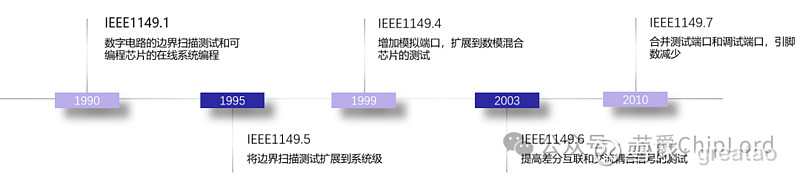

JTAG,全称为Joint Test Action Group,是一种用于测试集成电路的标准。它最初是为了在芯片封装后测试芯片内部连接及其功能的完整性,但随着技术的发展,JTAG被广泛应用于板级测试(PCB),并逐步成为系统级调试的重要工具。

1.1 背景介绍

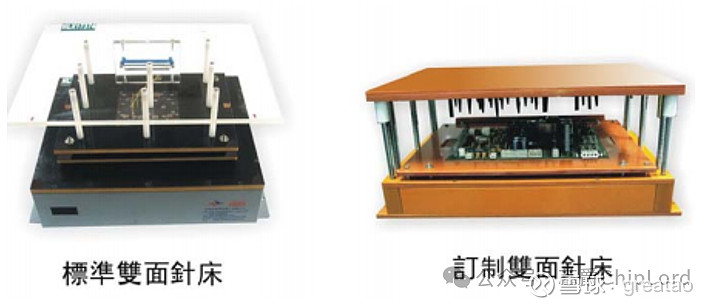

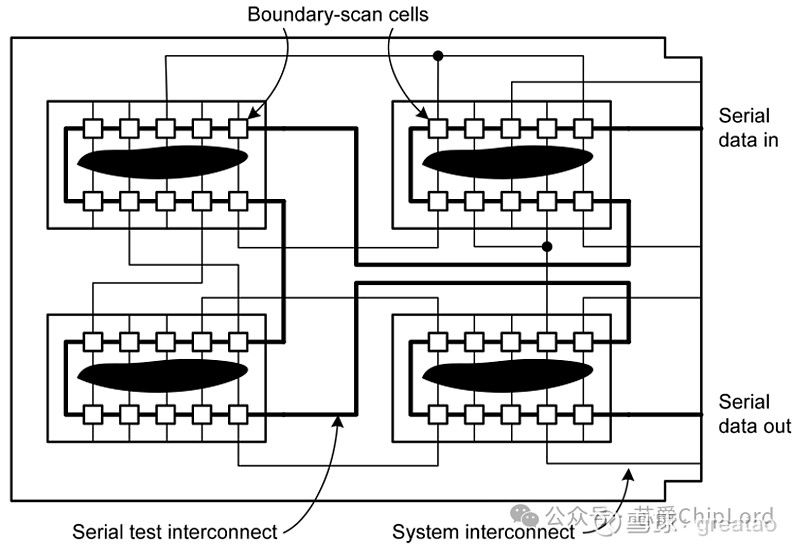

在传统的芯片测试中,通常采用针床测试的方法,但随着芯片管脚数量的增多和印刷电路板(PCB)的复杂性增加,传统方法已经逐渐无法满足需求。边界扫描测试(Boundary Scan)应运而生,成为解决这一问题的有效途径。JTAG通过在芯片内部设置测试逻辑单元,实现对芯片引脚及其互连的全面测试。

1.2 边界扫描测试的目的

边界扫描测试的主要目的是在不借助外部测试探针的情况下,对PCB上芯片间的互连进行测试。这种方法特别适用于复杂的多层板及密集封装的芯片,有效提高了测试效率和覆盖率。

二、JTAG的架构

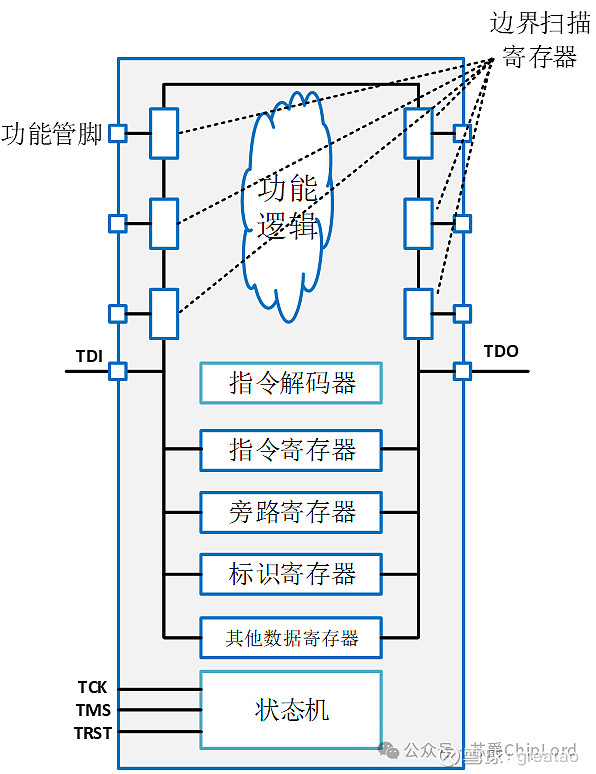

JTAG架构主要包括JTAG标准端口、JTAG状态机控制器和JTAG寄存器三个部分。

2.1 JTAG标准端口

JTAG标准端口通常包括以下信号:

TCK:测试时钟

TMS:测试模式选择

TDI:测试数据输入

TDO:测试数据输出

TRST(可选):测试复位

2.2 JTAG状态机控制器

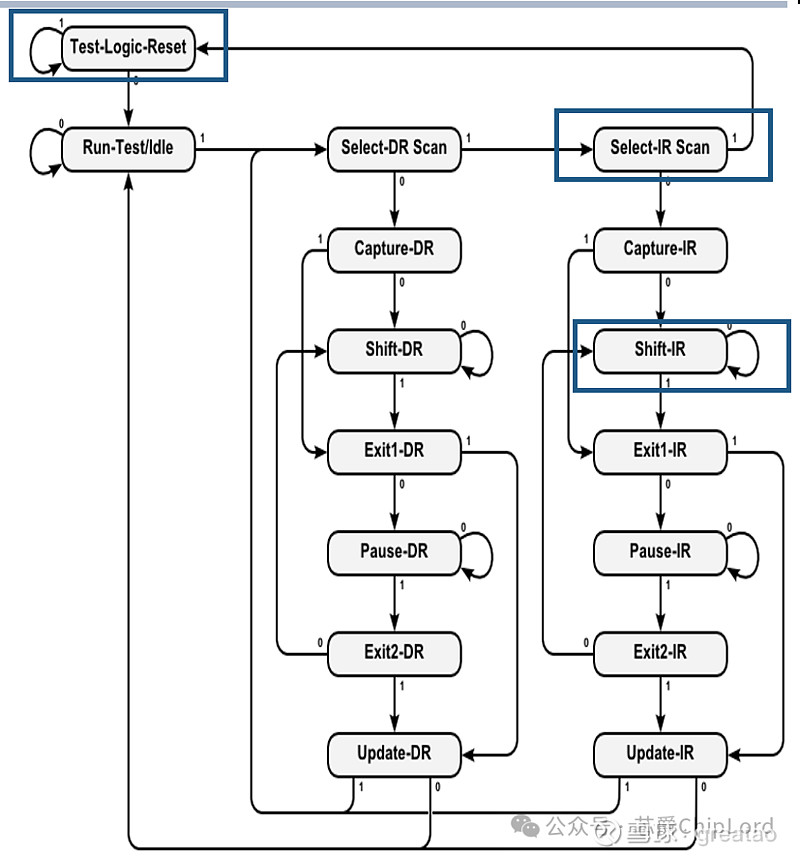

JTAG状态机控制器负责管理测试逻辑的状态转换。JTAG状态机通常有16个状态,通过TMS信号控制状态机的运转。

2.3 JTAG寄存器

JTAG寄存器包括指令寄存器和多个数据寄存器:

指令寄存器:存储JTAG指令

边界扫描寄存器:用于捕获和移位测试数据

旁路寄存器:用于旁路不需要测试的芯片,缩短测试时间

芯片标识寄存器:存储芯片的标识信息

三、JTAG的指令集

JTAG标准定义了一系列指令,用于不同的测试目的。以下是一些常用的JTAG指令:

EXTEST(必选):测试板级芯片间的互连线

BYPASS(必选):旁路不需要测试的芯片

SAMPLE(必选):获取芯片输入输出管脚上的即时数据

PRELOAD(必选):控制芯片输入输出管脚

IDCODE(可选):获取芯片ID信息

INTEST(可选):芯片内部测试

3.1 激活JTAG指令的方法

激活JTAG指令需要通过TMS信号运转状态机,依次进入Select-IR、Shift-IR和Run-Test/idle等状态,完成指令的加载和执行。

3.2 常用指令详解

EXTEST:该指令用于测试PCB上芯片之间的互连。测试序列包括输入EXTEST指令,通过TDI输入数据到芯片一,更新芯片一的输出管脚,芯片二捕获输入管脚数据,通过TDO输出数据。

BYPASS:该指令用于旁路不需要测试的芯片。TDI和TDO之间只有一个bit的旁路寄存器,有效缩短测试时间。

SAMPLE:该指令用于获取芯片输入输出管脚上的即时数据。

PRELOAD:该指令用于控制芯片输入输出管脚。

IDCODE:该指令用于获取芯片的ID信息。ID信息由32位组成,由JEDEC组织分配给每一个厂家。

四、Tessent边界扫描插入流程

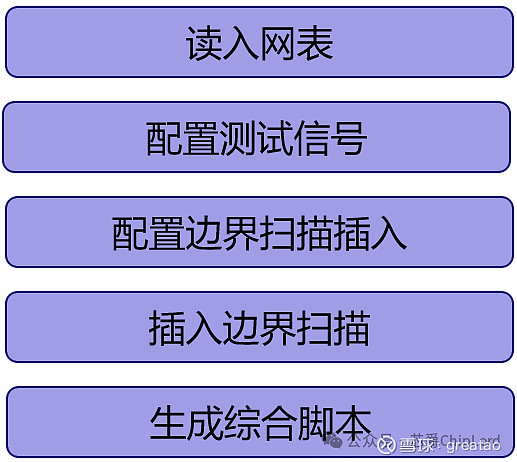

Tessent是一种用于自动插入边界扫描逻辑的工具。其边界扫描插入流程主要包括以下步骤:

4.1 读入网表

通过命令set_context dft –no_rtl读取网表,并设置当前设计。

4.2 配置测试信号

定义JTAG TAP引脚,并检查设计规则。

4.3 配置边界扫描插入

通过命令set_dft_specification_requirements –boundary_scan on配置边界扫描插入选项,生成相关配置数据。

4.4 插入边界扫描

处理DFT规范,生成相应的RTL,并插入现有网表,检查连接并生成ICL文件及时序约束文件。

4.5 生成综合脚本

在Tessent shell内部调用综合工具,生成综合脚本,并在外部调用综合工具完成设计综合。

总结

JTAG技术在芯片测试领域发挥着至关重要的作用。通过深入了解JTAG的概念、架构、指令集及其在边界扫描测试中的应用,可以帮助我们更好地进行芯片测试和系统调试。希望本文对您理解和应用JTAG技术有所帮助。

更多DFT专业知识在知识星球。

长按 识别图中二维码即可关注